Hi,

I am working on design, that uses ES9038Q2M as auxiliary DAC chip. I am attempting to run its in synchronous mode, however it is constantly misbehaving.

The system is as follows:

-MCLK is 22.5792/24.576MHz, delivered from low jitter clock distribution directly to the DAC chip.

-Signal source is on board XU208, LRCK and BCLK are delivered directly to DAC chip via short, impedance matched traces (signal integrity is perfect, as far as my 500MHz scope can measure).

-Interface is set to 32 bit I2S.

I am attempting following configuration:

-In register 10, I am setting 128fs mode bit to enabled

-Register 12 is set to 0 (DPLL disabled)

-Register 1 is set to 0xC0 (32 bit input, standard I2S mode, force fixed input type, input type SERIAL)

-Register 6 is set to 0x00 (linear phase fast roll-off filter), but leaving it on default values have no effect

-Register 15 and 16 are set to 0x00 (full volume).

-Register 14 is set to enable soft start and begin outputting analog signal.

During sample rate changes, I am attempting to set Reg 0 CLK_GEAR to value that always matches 128*fs relationship, that is:

-0b10 for 44.1/48ksps

-0b01 for 88.2/96ksps

-0b00 for 192/176.4ksps

However, resultant DAC behavior is clearly abnormal, that is - produced spectral response is completely skewed.

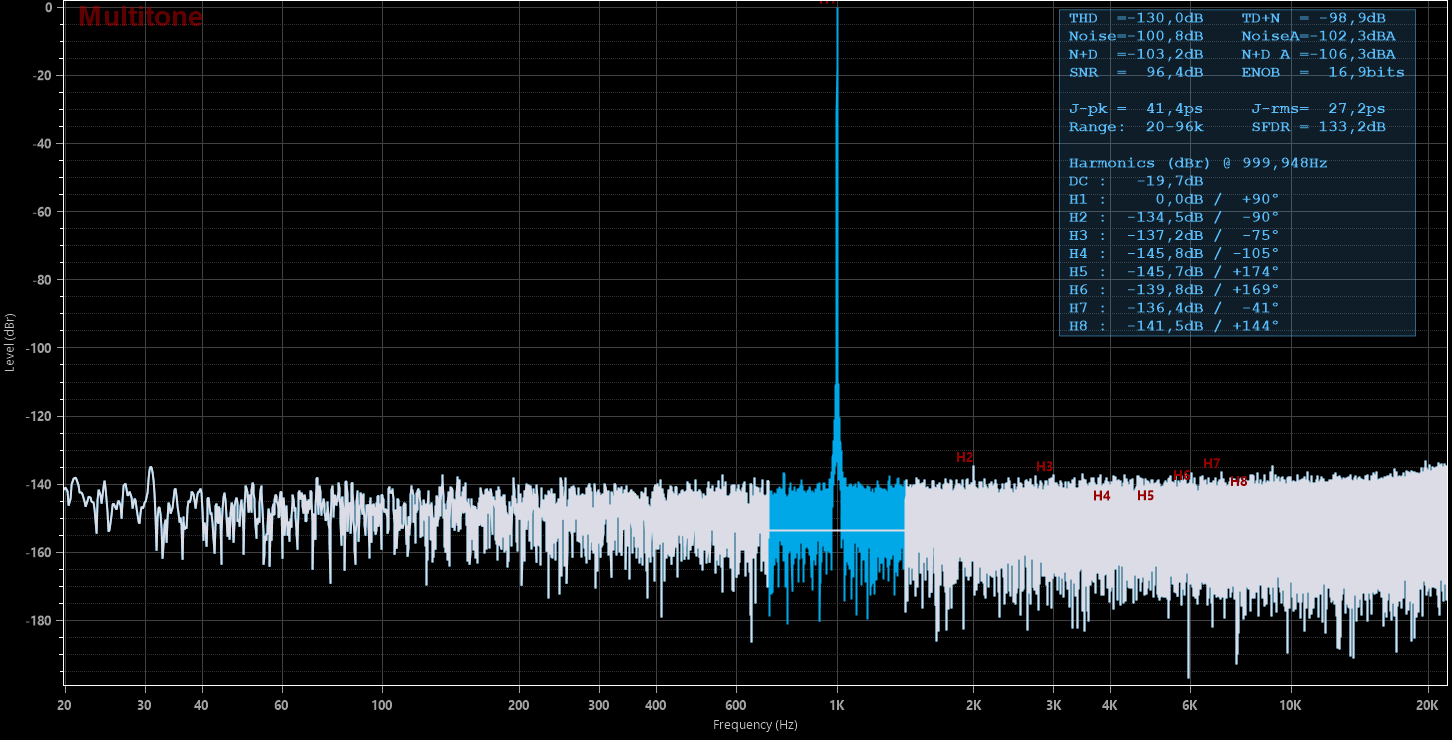

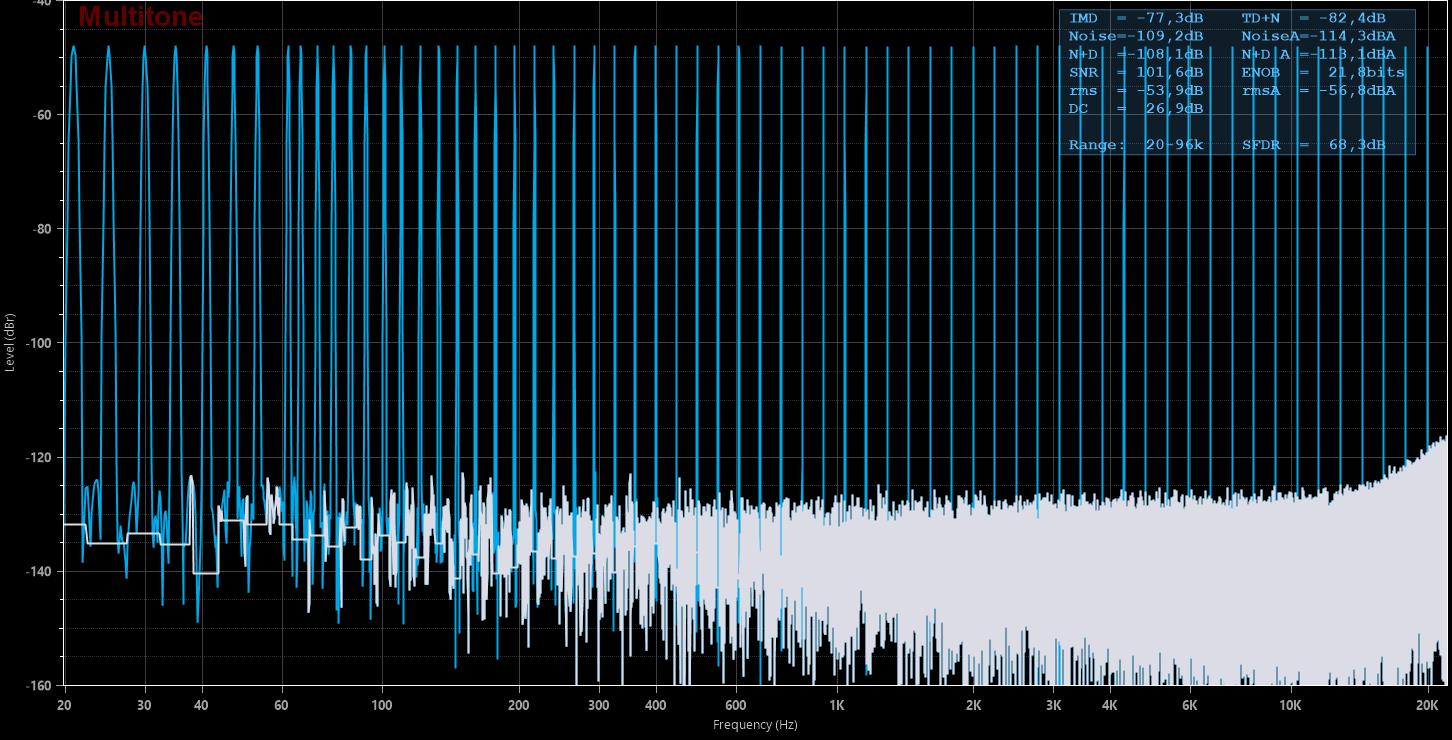

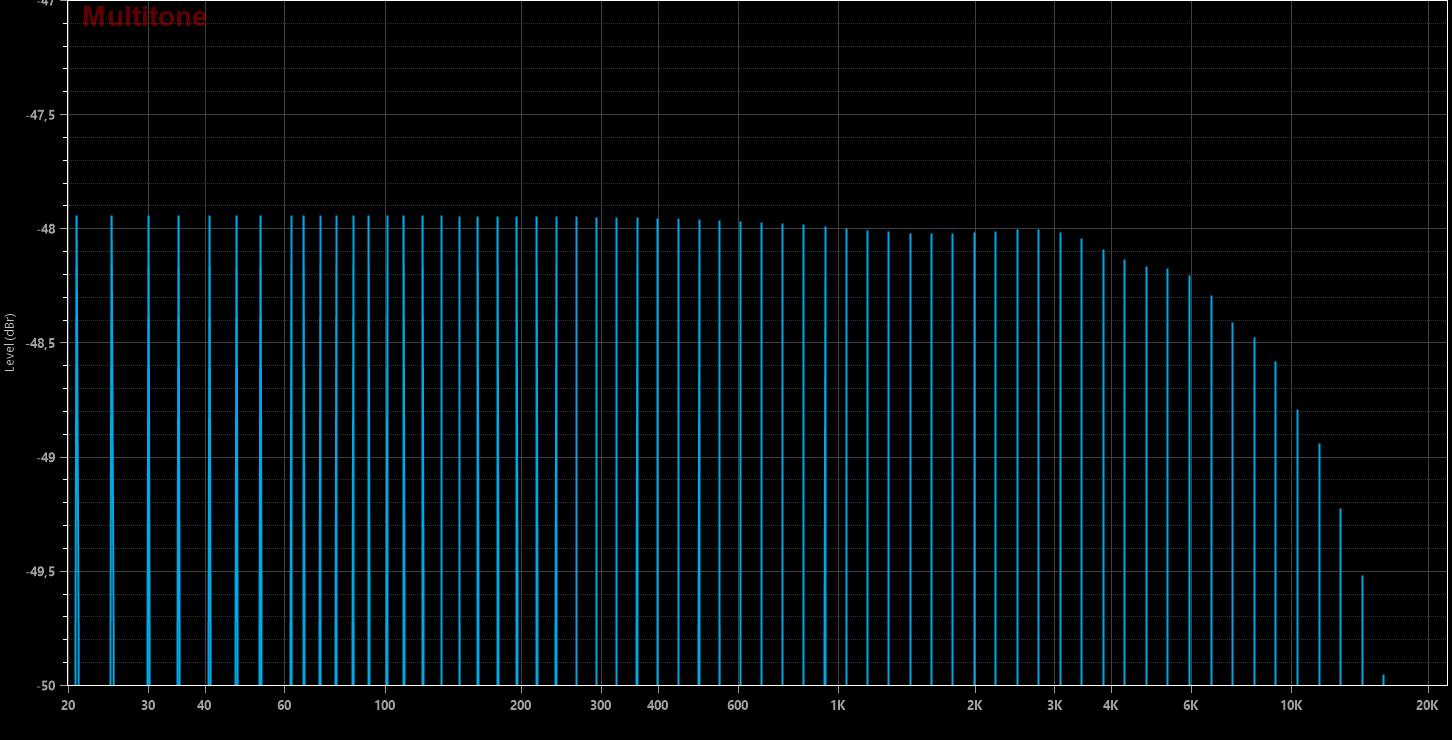

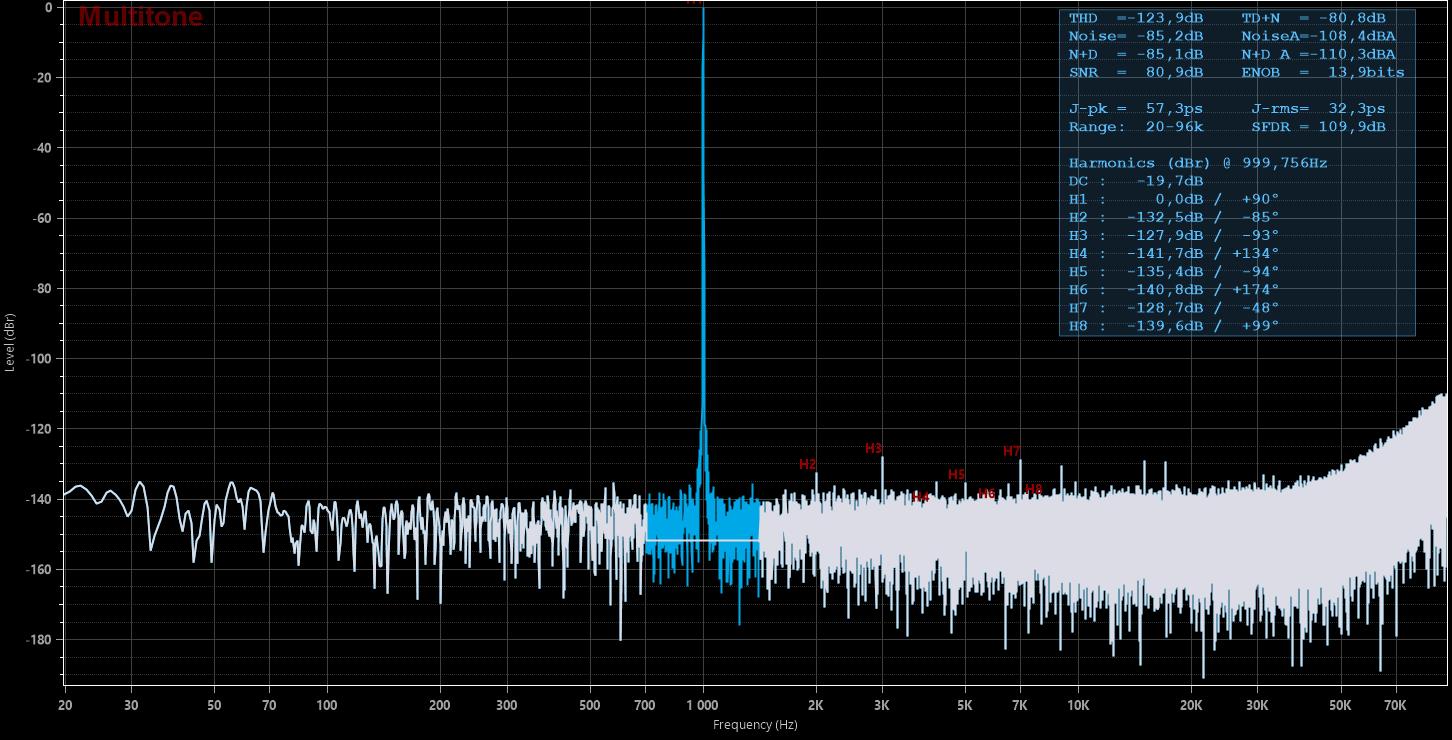

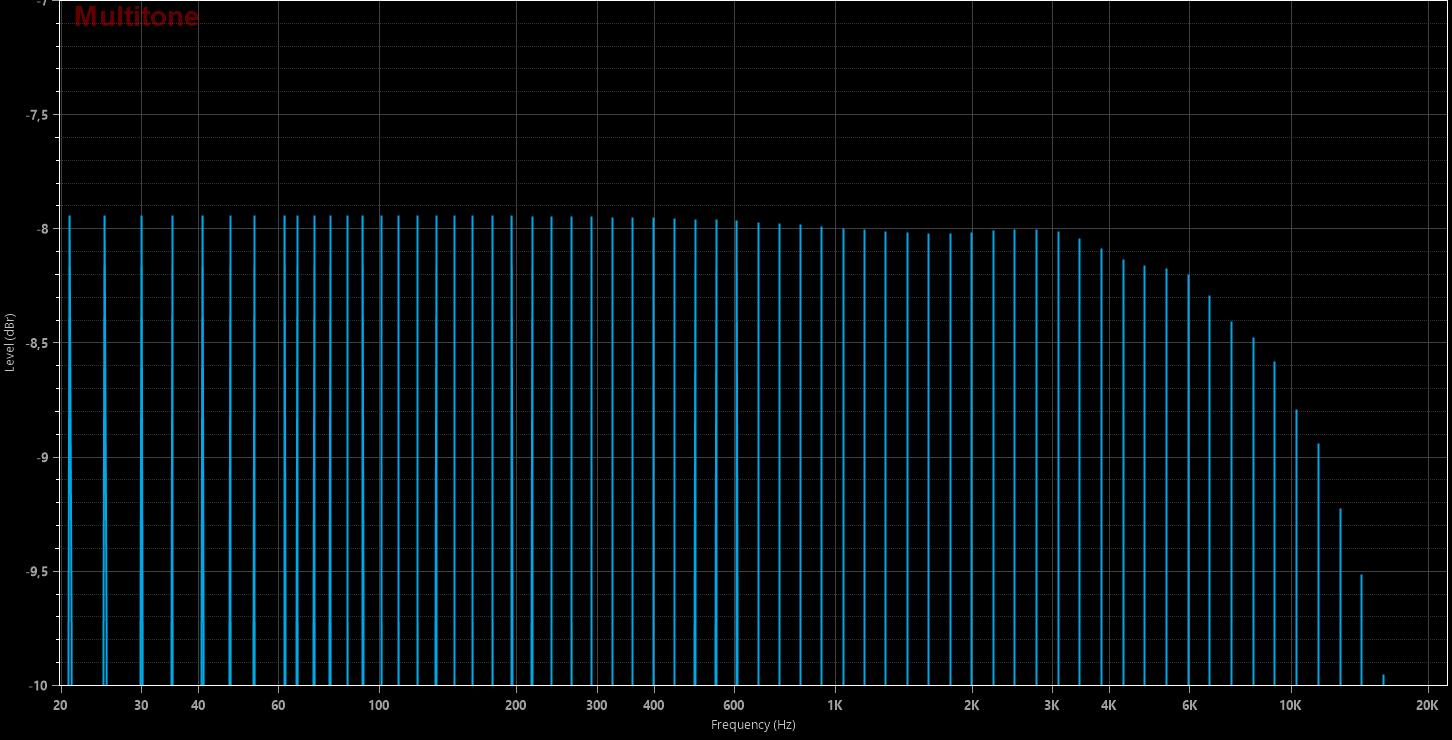

For 44.1/48, both distortion and bandwidth are excellent:

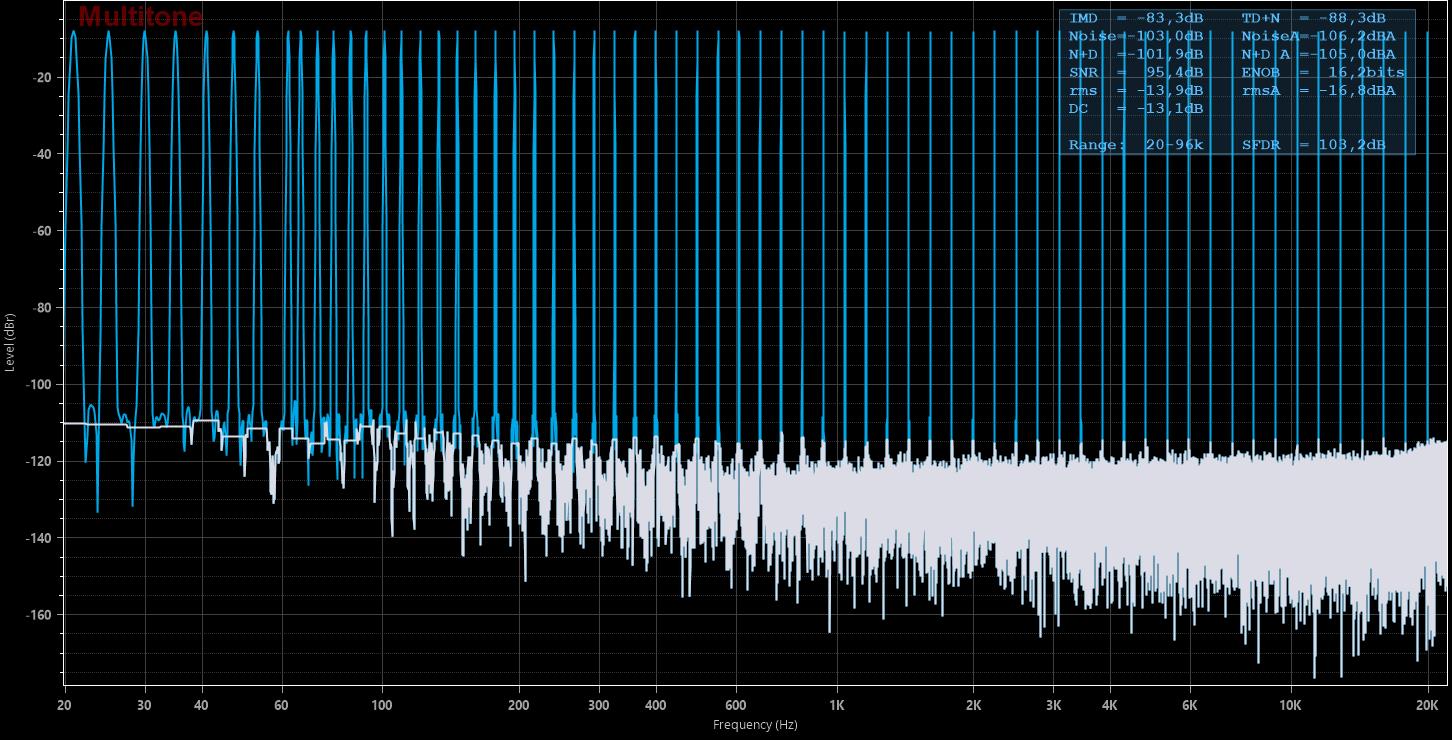

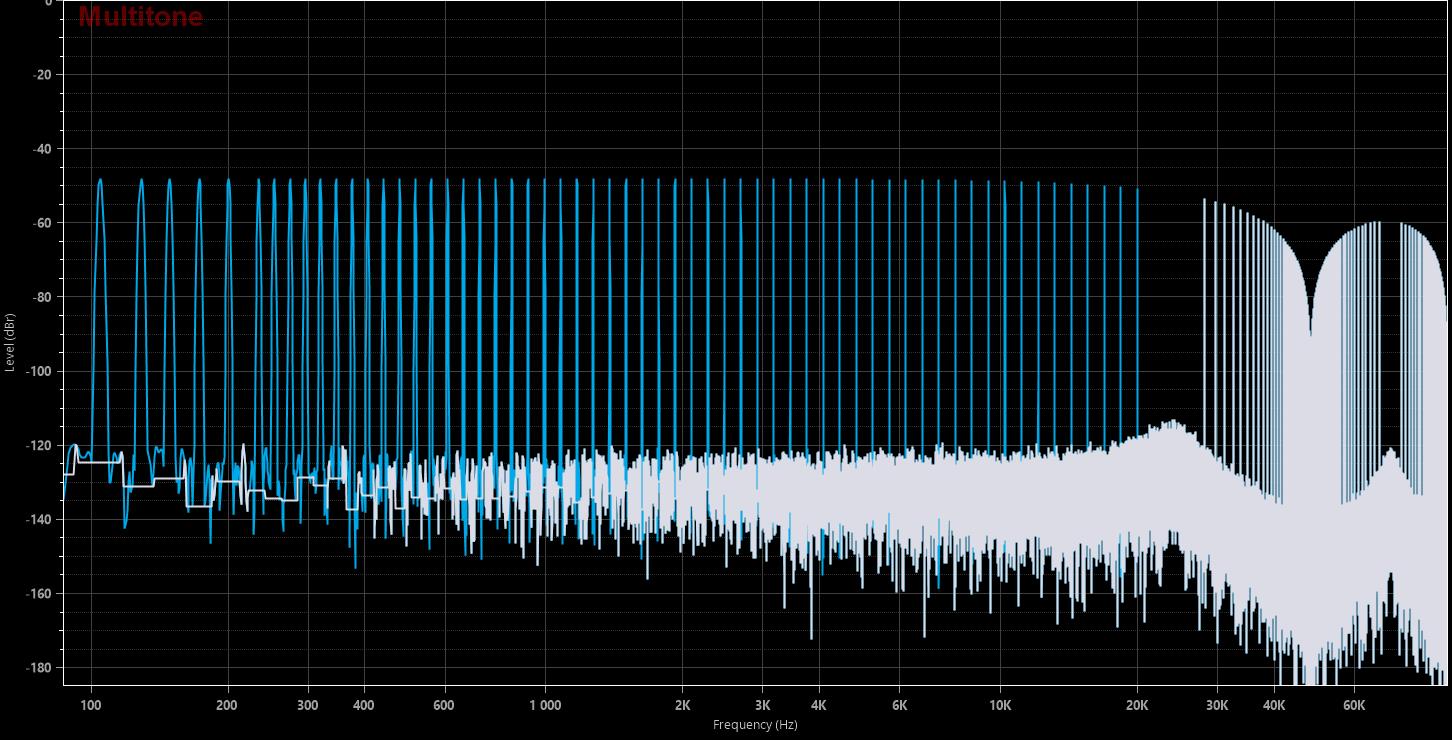

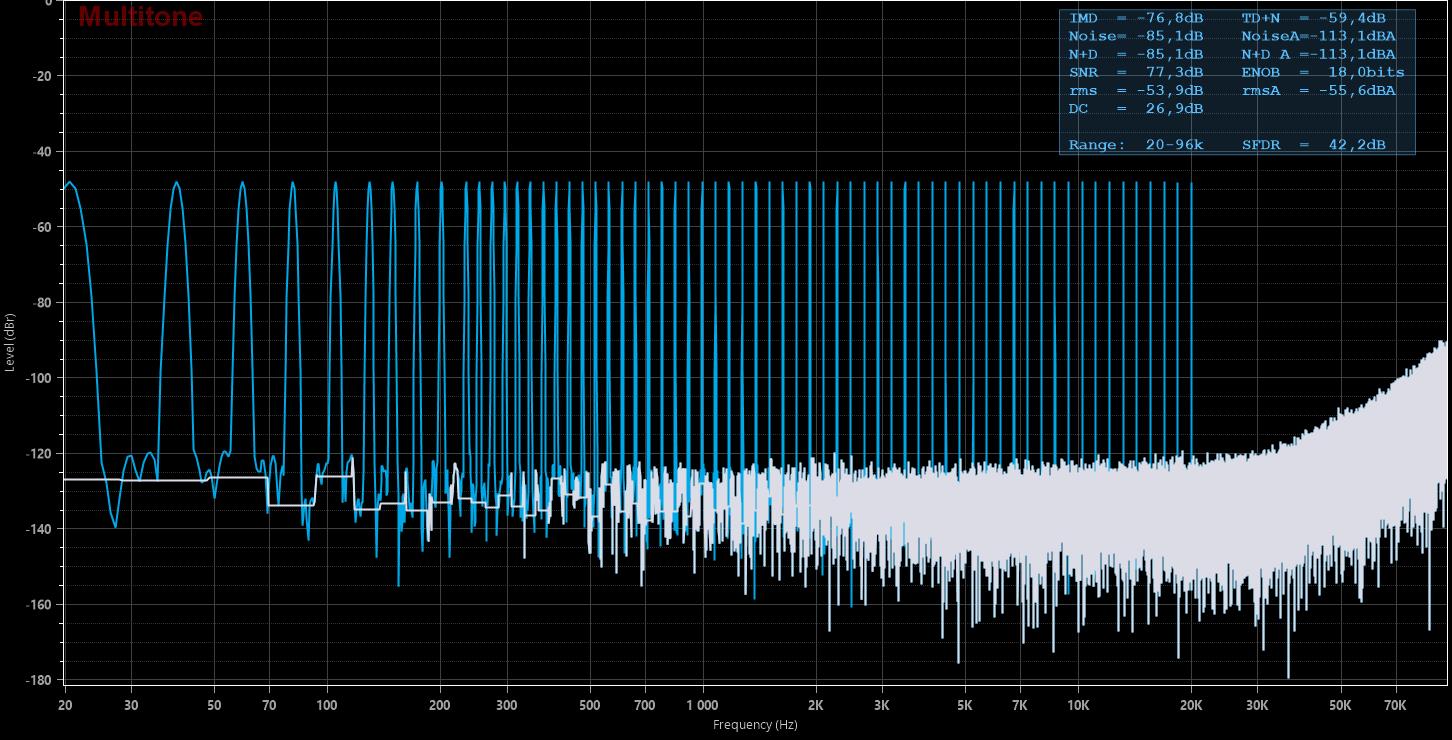

However, for any higher sample rate, two problems appear. First, the bandwidth fall to -3db at 20kHz, second - massive aliasing appears out of band:

So, I have realized i have not set ASRC disable bit in the register 27. I have done so, and it caused even worse problems.

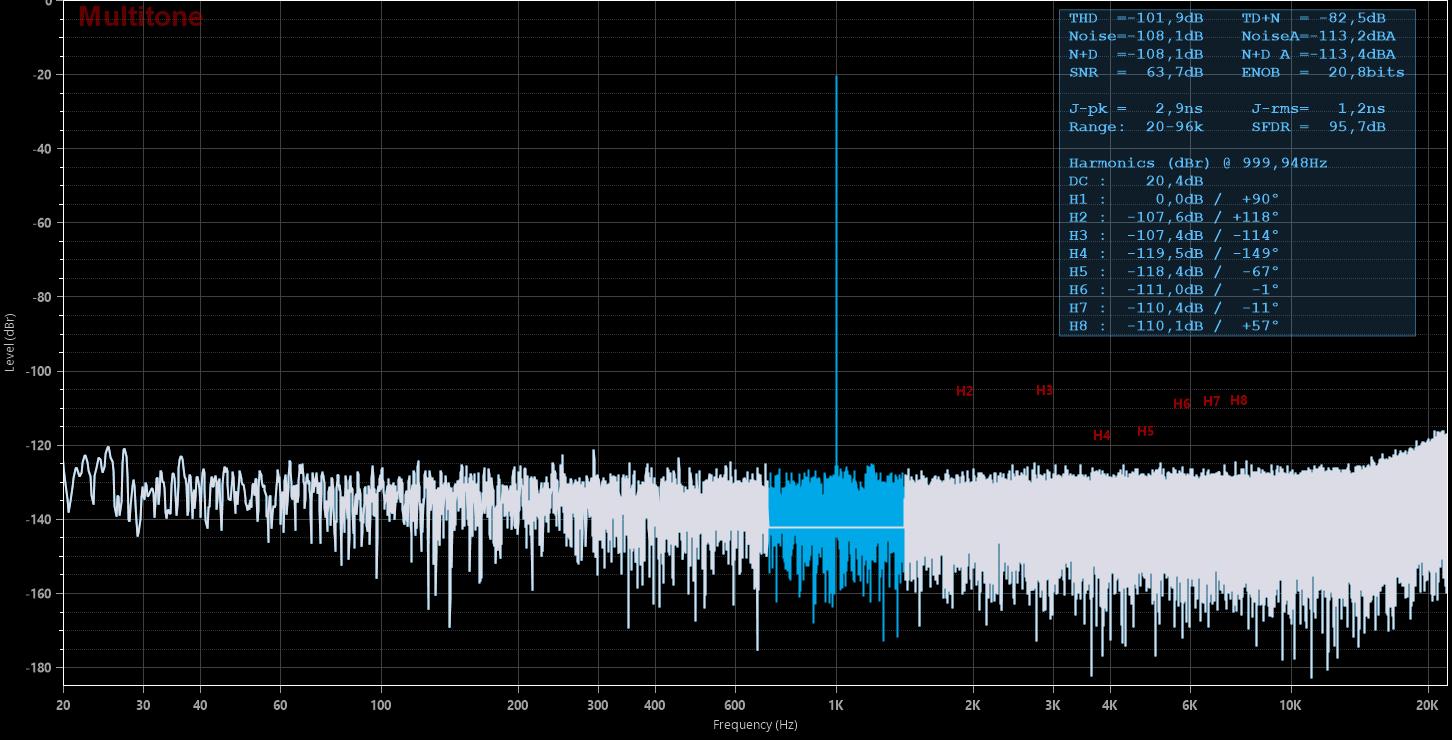

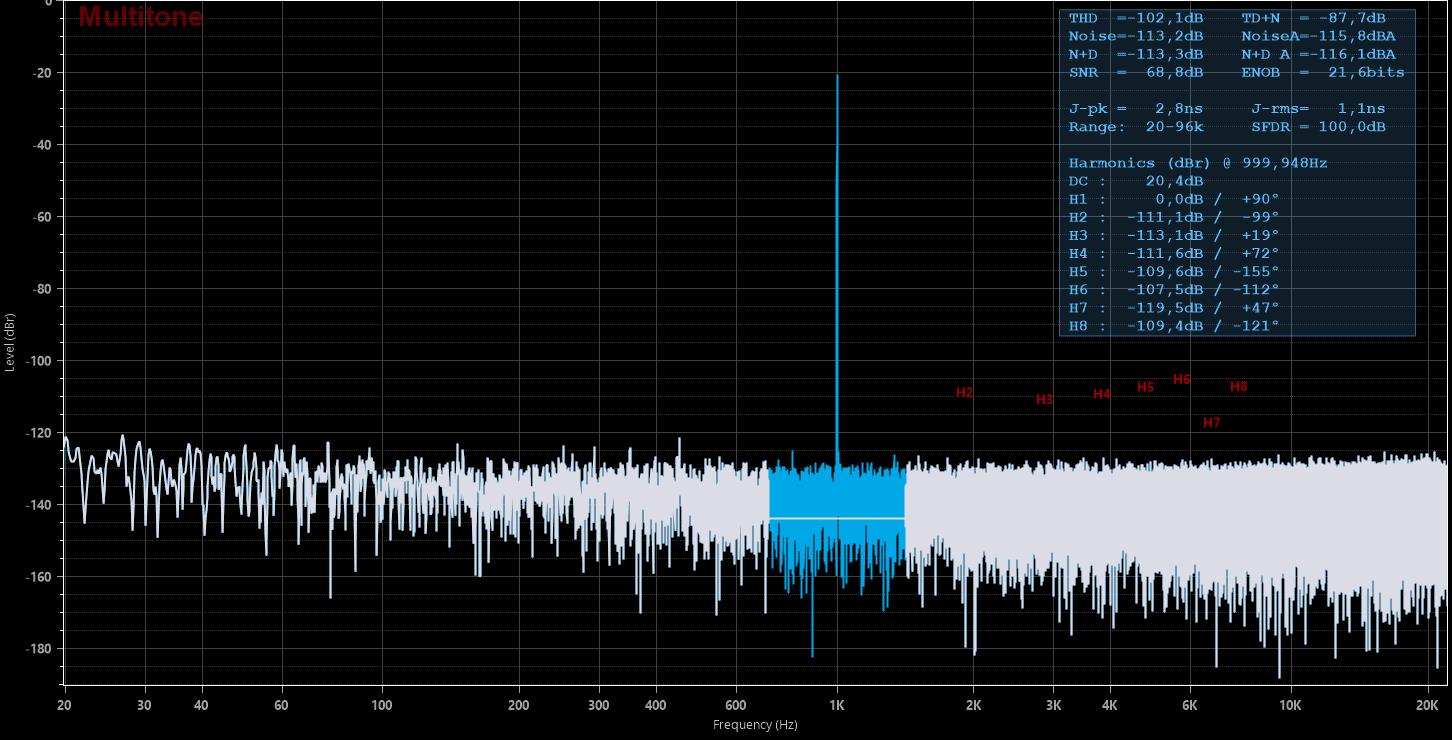

At 44.1ksps, there is no gain loss at 20kHz, however - noise floor is massively elevated, and 0dbfs output became limited to -20db.

At 192ksps, we still have aliases and too fast roll-off, along with reduced full scale amplitude.

So, as a next step, I have decided to disable clock gearing and leave it at 0b00 (full input clock frequency) regardless of sample rate.

Now, at 44.1ksps, noise floor is elevated, 0dbfs is limited by 20db, and there is roll-off at 20khz.

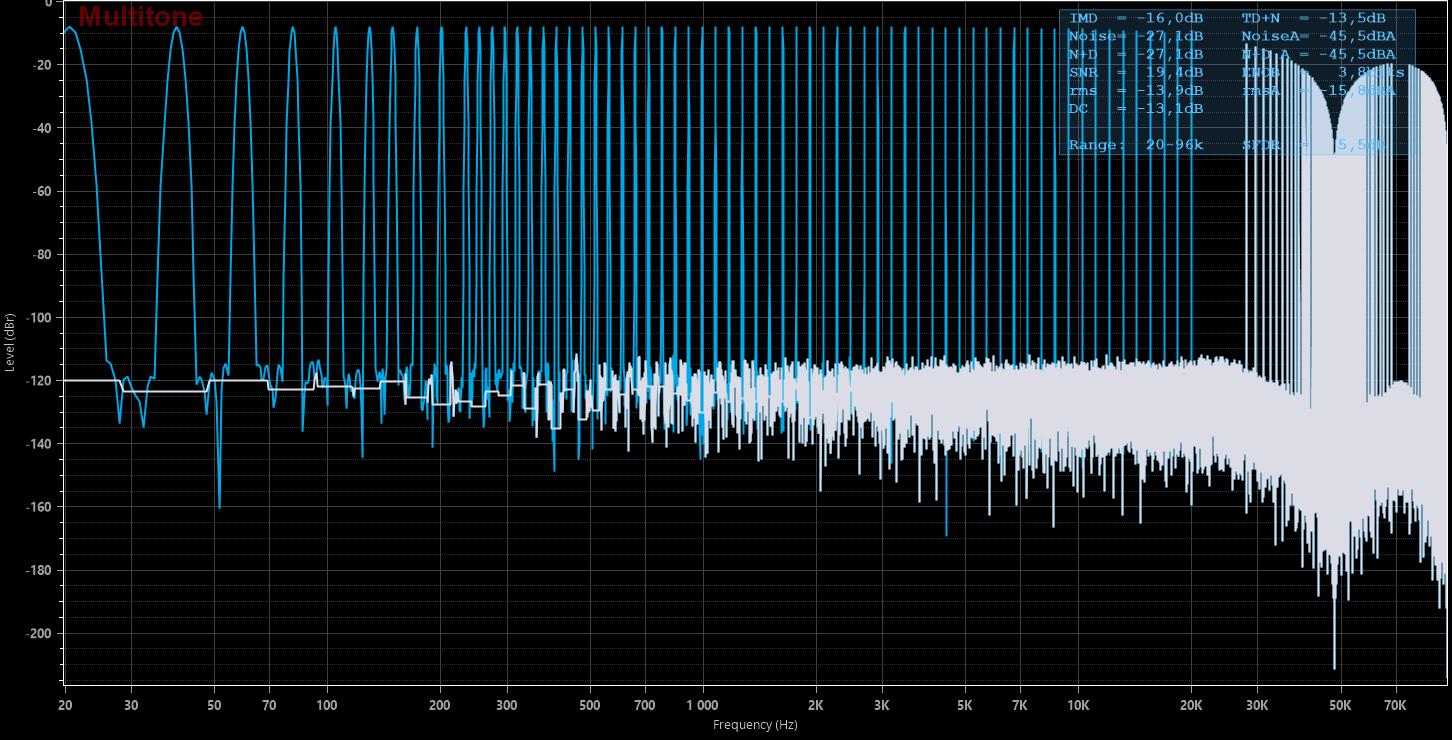

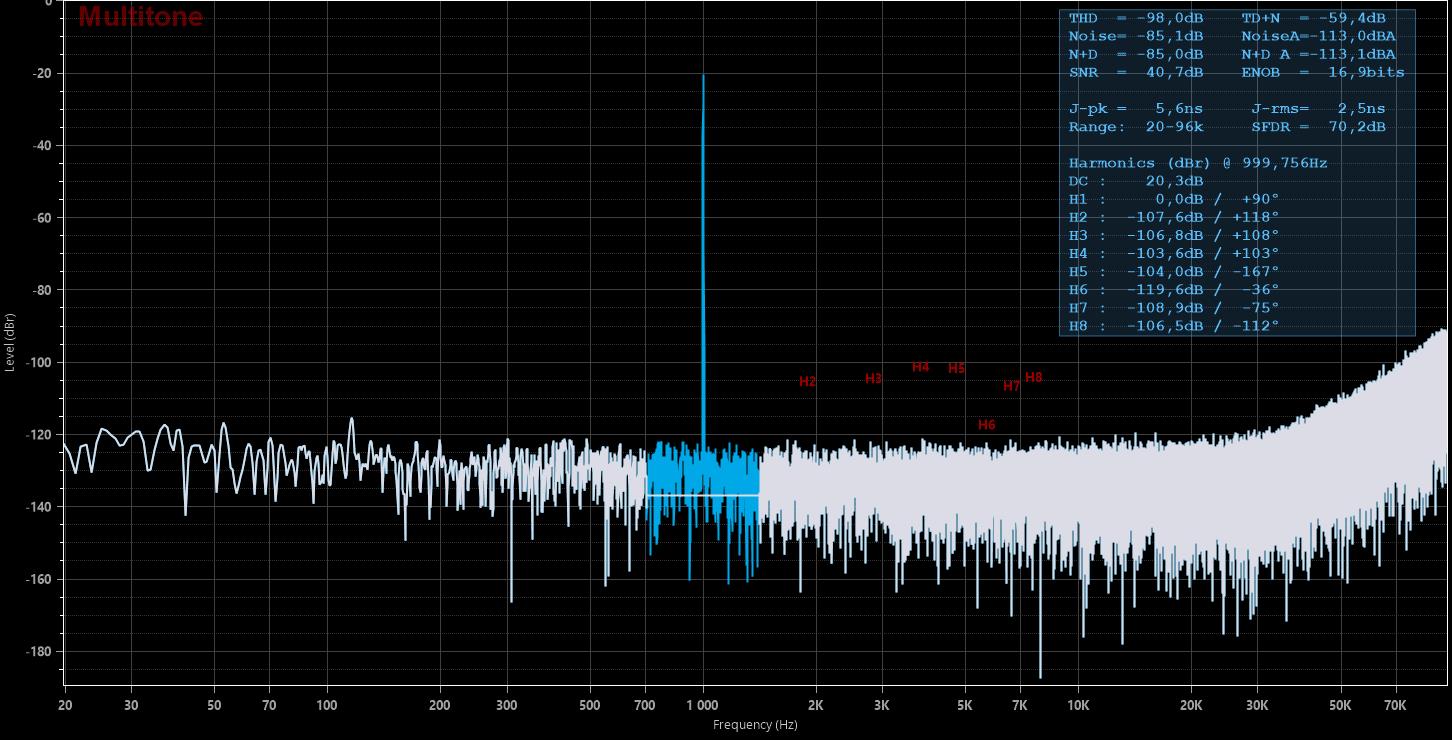

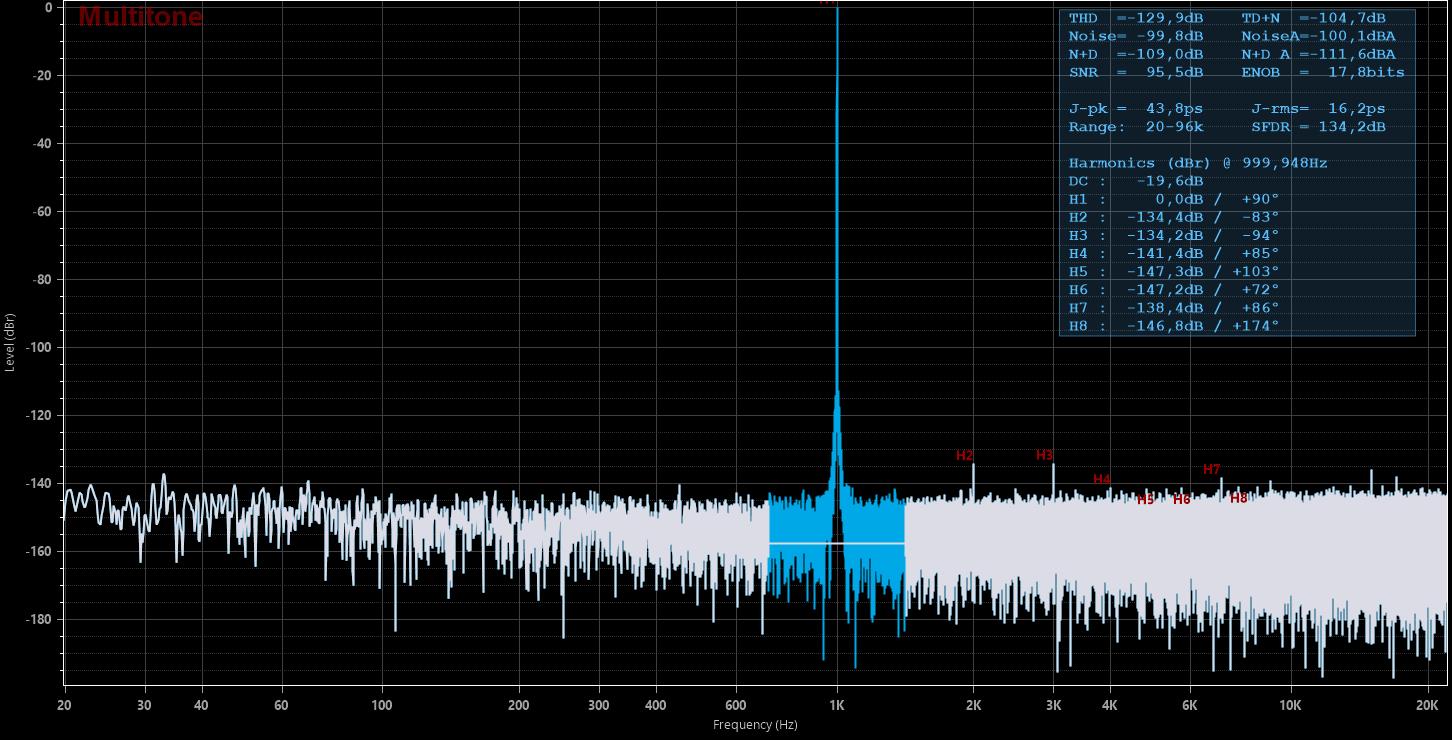

At 192ksps, 0dbfs point of DAC is still reduced by 20db, noise floor is still elevated, but there is no drop at 20kHz and no aliasing:

Lacking any idea what this chip tries to do, I have decided to leave clock gear fixed at 0b00, but enable ASRC (reg 27 bit 7 set to 1).

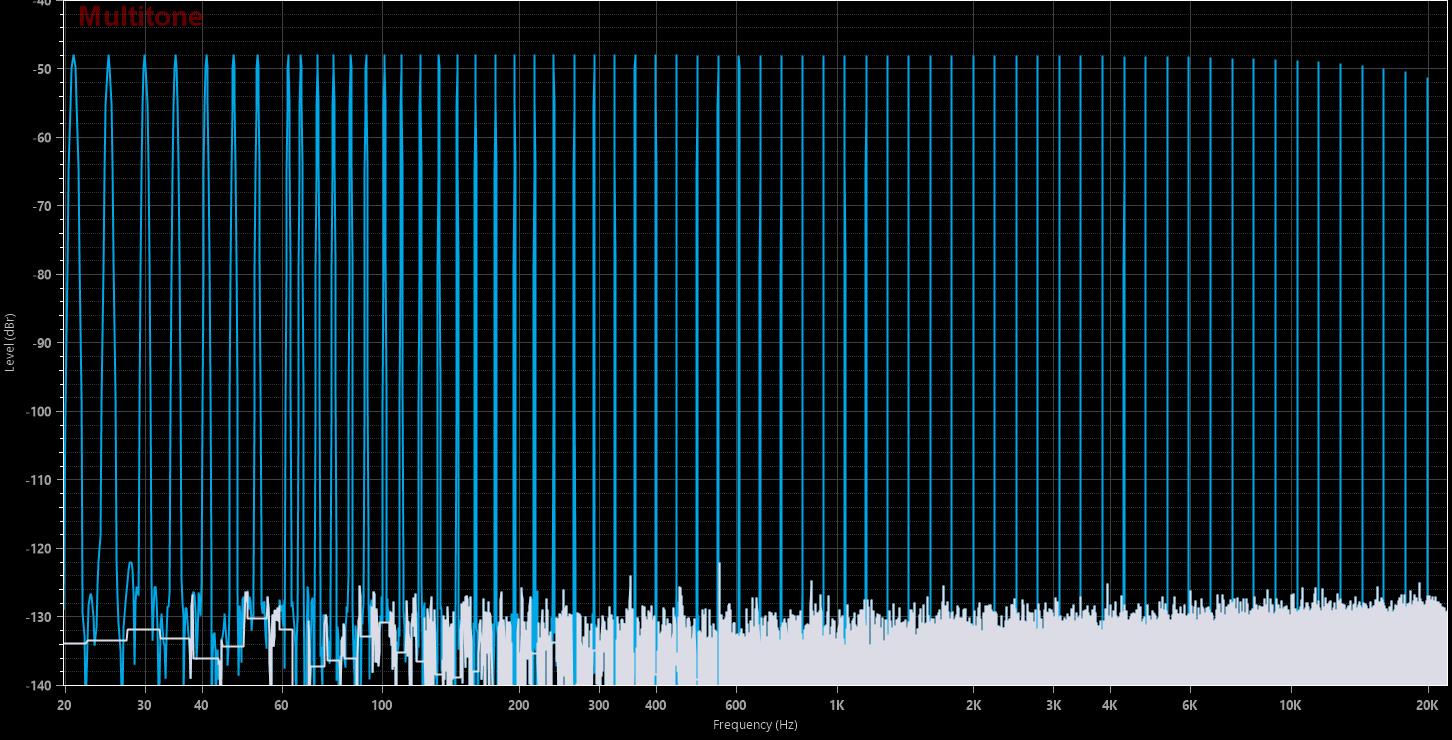

Now, at 192ksps everything works properly. No elevated noise floor, no 20kHz drop, no aliases and 0dbfs input produces full scale on DAC output.

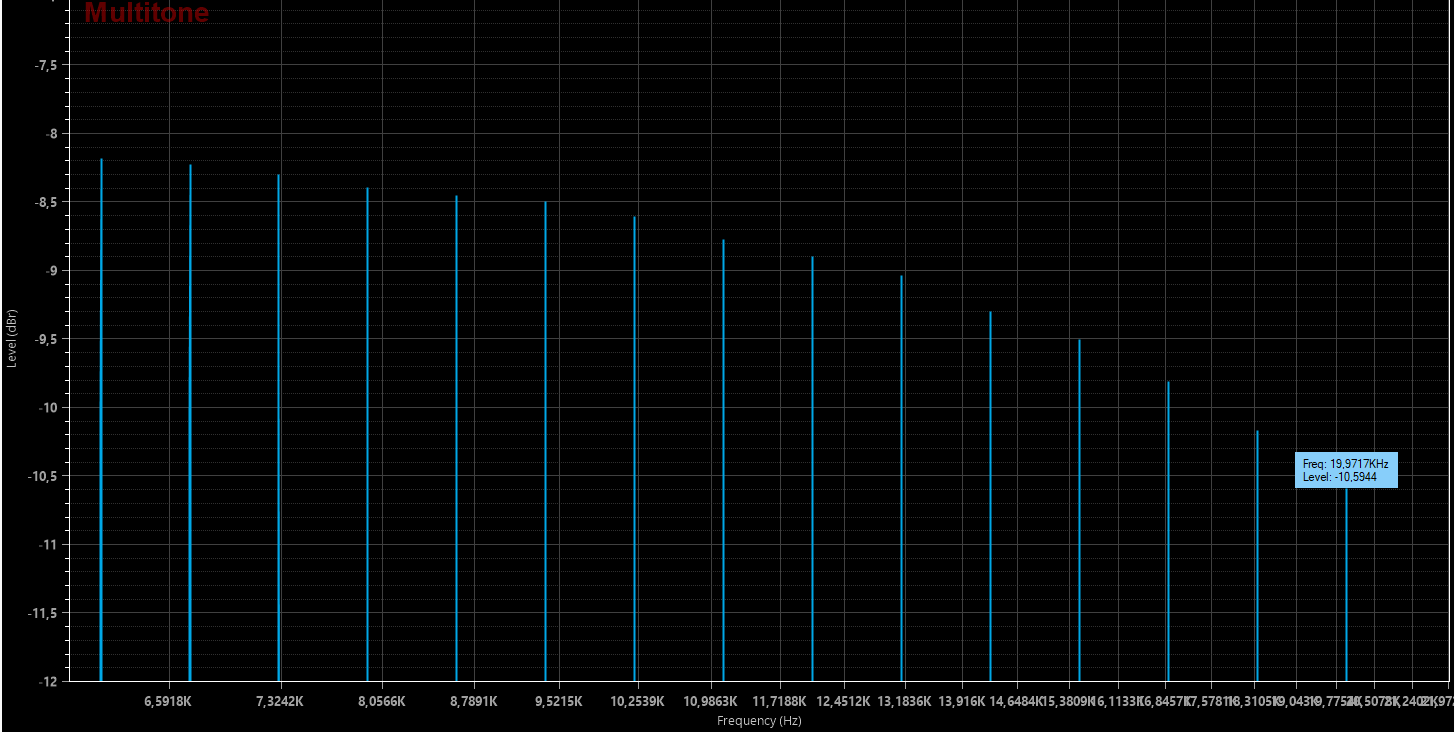

But on 44.1ksps, while all other problems disappear, 20kHz drops have appeared.

Honestly, I am stumped. Does anyone have experience with implementing synchronous mode in this chip, and can suggest what I am missing?

I am happy to provide any additional information.

Best regards

I am working on design, that uses ES9038Q2M as auxiliary DAC chip. I am attempting to run its in synchronous mode, however it is constantly misbehaving.

The system is as follows:

-MCLK is 22.5792/24.576MHz, delivered from low jitter clock distribution directly to the DAC chip.

-Signal source is on board XU208, LRCK and BCLK are delivered directly to DAC chip via short, impedance matched traces (signal integrity is perfect, as far as my 500MHz scope can measure).

-Interface is set to 32 bit I2S.

I am attempting following configuration:

-In register 10, I am setting 128fs mode bit to enabled

-Register 12 is set to 0 (DPLL disabled)

-Register 1 is set to 0xC0 (32 bit input, standard I2S mode, force fixed input type, input type SERIAL)

-Register 6 is set to 0x00 (linear phase fast roll-off filter), but leaving it on default values have no effect

-Register 15 and 16 are set to 0x00 (full volume).

-Register 14 is set to enable soft start and begin outputting analog signal.

During sample rate changes, I am attempting to set Reg 0 CLK_GEAR to value that always matches 128*fs relationship, that is:

-0b10 for 44.1/48ksps

-0b01 for 88.2/96ksps

-0b00 for 192/176.4ksps

However, resultant DAC behavior is clearly abnormal, that is - produced spectral response is completely skewed.

For 44.1/48, both distortion and bandwidth are excellent:

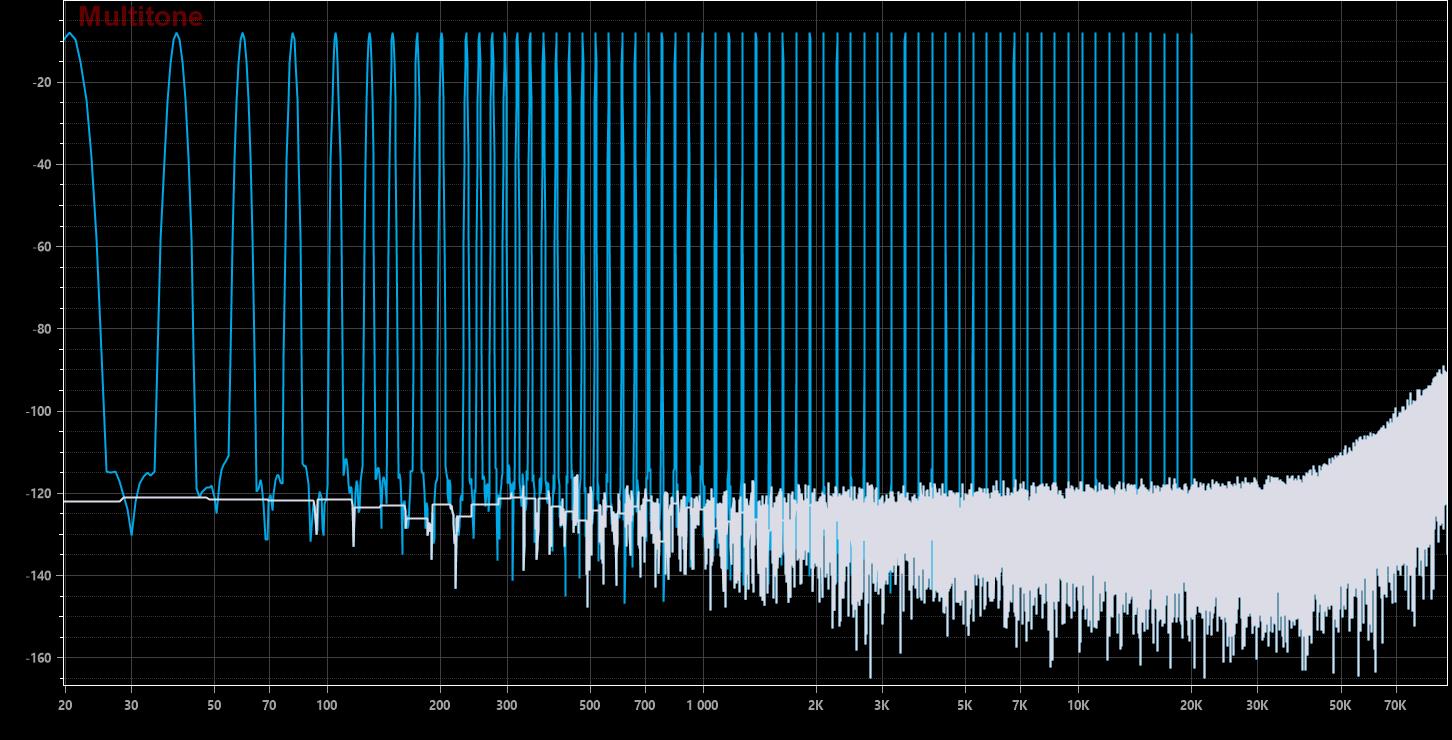

However, for any higher sample rate, two problems appear. First, the bandwidth fall to -3db at 20kHz, second - massive aliasing appears out of band:

So, I have realized i have not set ASRC disable bit in the register 27. I have done so, and it caused even worse problems.

At 44.1ksps, there is no gain loss at 20kHz, however - noise floor is massively elevated, and 0dbfs output became limited to -20db.

At 192ksps, we still have aliases and too fast roll-off, along with reduced full scale amplitude.

So, as a next step, I have decided to disable clock gearing and leave it at 0b00 (full input clock frequency) regardless of sample rate.

Now, at 44.1ksps, noise floor is elevated, 0dbfs is limited by 20db, and there is roll-off at 20khz.

At 192ksps, 0dbfs point of DAC is still reduced by 20db, noise floor is still elevated, but there is no drop at 20kHz and no aliasing:

Lacking any idea what this chip tries to do, I have decided to leave clock gear fixed at 0b00, but enable ASRC (reg 27 bit 7 set to 1).

Now, at 192ksps everything works properly. No elevated noise floor, no 20kHz drop, no aliases and 0dbfs input produces full scale on DAC output.

But on 44.1ksps, while all other problems disappear, 20kHz drops have appeared.

Honestly, I am stumped. Does anyone have experience with implementing synchronous mode in this chip, and can suggest what I am missing?

I am happy to provide any additional information.

Best regards

I have a similar setup, with the same MCLK frequencies.

My settings are as follows:

Register 0: 0x00 (default)

Register 6: 0x42 (default)

Register 10:

0x12 for sample rate = 192/176.4

0x02 for sample rates < 192/176.4

Register 12: 0x5A (default)

I have set register 1 to 0x80, but that is probably not important, since I would expect 0xC0 to give the same result.

I think you should only set the 128fs bit mode when using the high sample rates.

I left the PLL ON, but whether that makes a difference, I don’t know.

You mention register 6, but I assume that you meant register 7, since register 7 is the one controlling the filter settings.

My settings are as follows:

Register 0: 0x00 (default)

Register 6: 0x42 (default)

Register 10:

0x12 for sample rate = 192/176.4

0x02 for sample rates < 192/176.4

Register 12: 0x5A (default)

I have set register 1 to 0x80, but that is probably not important, since I would expect 0xC0 to give the same result.

I think you should only set the 128fs bit mode when using the high sample rates.

I left the PLL ON, but whether that makes a difference, I don’t know.

You mention register 6, but I assume that you meant register 7, since register 7 is the one controlling the filter settings.

Thank you JensH, I had similar idea, but was determined to run the DAC fully synchronously.

But as you say - if 128fs bit is set only when MCLK fed into ESS chip is actually 128*fs (192/176.4ksps) and for all other ESS is left to run asynchronously everything works perfectly.

This implies, that MCLK divider does not work properly in synchronous mode - which does not surprise me, my experience so far suggest that ESS chips ale full of misbehaving features. I suppose, with external clock divider this DAC could be run in "true" synchronous mode, but at this point - I doubt it is worth the effort.

It seems it have to run in sync/async hybrid like that.

But as you say - if 128fs bit is set only when MCLK fed into ESS chip is actually 128*fs (192/176.4ksps) and for all other ESS is left to run asynchronously everything works perfectly.

This implies, that MCLK divider does not work properly in synchronous mode - which does not surprise me, my experience so far suggest that ESS chips ale full of misbehaving features. I suppose, with external clock divider this DAC could be run in "true" synchronous mode, but at this point - I doubt it is worth the effort.

It seems it have to run in sync/async hybrid like that.